Recently, there has been an increasing attention to EDA tools in the chip industry. In this regard, iSTART-TEK stated that EDA tools are the foundation of the IC industry. In the ever-changing global industries, to avoid bottlenecks in the IC design process, businesses and nations are more concerned about having independent and controllable EDA tools.

The U. S. government has implemented strict export controls since August 15, 2022. Before that, the U. S. also launched the “CHIPS and Science Act 2022”, which was to cut off the supply of advanced process technologies, equipment, and materials to China. With government subsidies, the U. S. planned to attract the IC companies to return. Furthermore, the U. S. prohibited China from purchasing advanced process chips and chip manufacturing equipment on October 7, 2022.

According to the analysis of iSTART-TEK, in the post-Moore era, chip design complexity has increased, and chips are becoming increasingly small, causing R&D and manufacturing costs to gradually rise. On the other hand, there are strong demands of AI, IoT, automotive electronics and large-scale computing-related applications, making the development cost of high-end chips made from advanced processes more expensive. That is why EDA tools are essential in shortening chip development cycle and reducing chip design costs.

iSTART-TEK emphasizes that EDA (Electronic Design Automation) indicates the use of computer-aided design (CAD) software to complete the functional design, synthesis, verification, and physical design of IC chips, including layout, wiring, and layout designs. Therefore, EDA tools are widely applied in IC design, manufacturing and packaging.

The fast-paced global IC industry provides a huge growth potential for the EDA tool market. In the recent years, the complexity of IC design and manufacturing processes has increased due to advances in IC manufacturing. This has led to a greater demand for EDA tools and the growth of the global EDA market. EDA tools have become crucial in IC design.

As the leading provider of EDA tools and IPs, iSTART-TEK specializes in memory testing and repair technologies that are widely adopted by domestic and international IC design and service companies. The company’s unique and patented memory testing and repair technologies along with real-time technical support bring low-power-consumption, low-cost and high-efficiency solutions to the entire IC product lifecycle, from design to mass production.

iSTART-TEK has had a long-standing involvement in the EDA field. With high-performance memory repair technologies and diverse memory testing algorithms, the company’s comprehensive memory testing and repair services have benefited IC design companies, design service companies and semiconductor foundries. By closely collaborating with the design and design service ends, iSTART-TEK’s solutions can help enhance the chip performance, stability and yield, and further accelerate time-to-market. In addition, the company’s total solutions have been successfully applied in the advanced processes ranging from 180nm to 7nm.

Since its establishment, iSTART-TEK has constantly created values for customers with its philosophy of independent patents and technologies. iSTART-TEK ‘s high-performance memory repair technology and memory testing algorithms have been recognized by many well-known IC design companies in Taiwan, China and South Korea. Many of these companies have also signed contracts with iSTART-TEK that include royalty payments.

iSTART-TEK said that its diverse algorithms, patented architectures and customized services are its core competitive edges that enable it to differentiate itself from the competitors. In terms of core technologies, iSTART-TEK has developed EDA tools including START™ v3, EZ-BIST, and EZ-NBIST specifically for IC design and design service companies. Through its deep technology accumulation, rich practical experience, and strong market foundation, the company has continually developed innovative products that greatly improve chip yield, lower chip development costs, and reduce memory repair time. All these contributions have boosted the development of the IC industries.

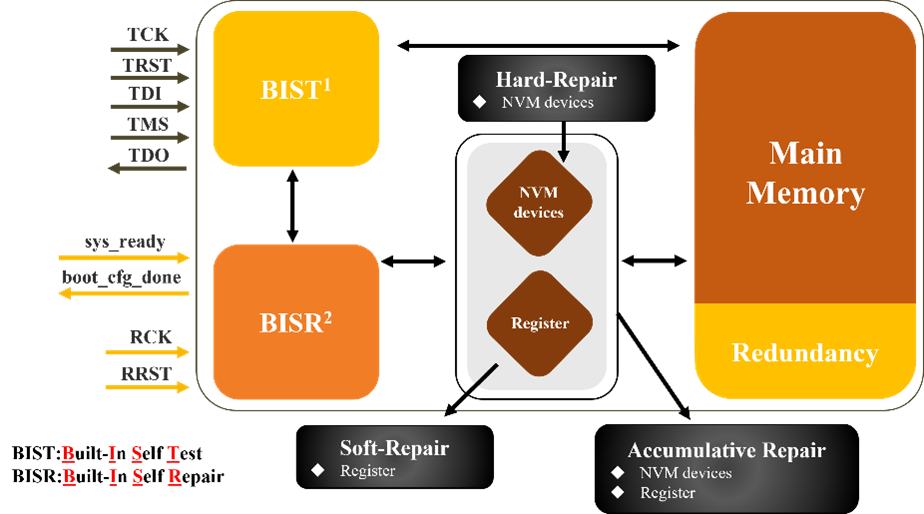

START™ v3 (a memory testing and repair circuit development environment) contains two types of memory repair technologies, Hard Repair and Soft Repair. Hard Repair requires a non-volatile memory (NVM) as the component to record the memory error information. This feature can greatly shorten the memory repair time. Soft Repair does not require an NVM to record the memory error information. When there are enough backup memories, Soft Repair can repetitively perform the memory repair.

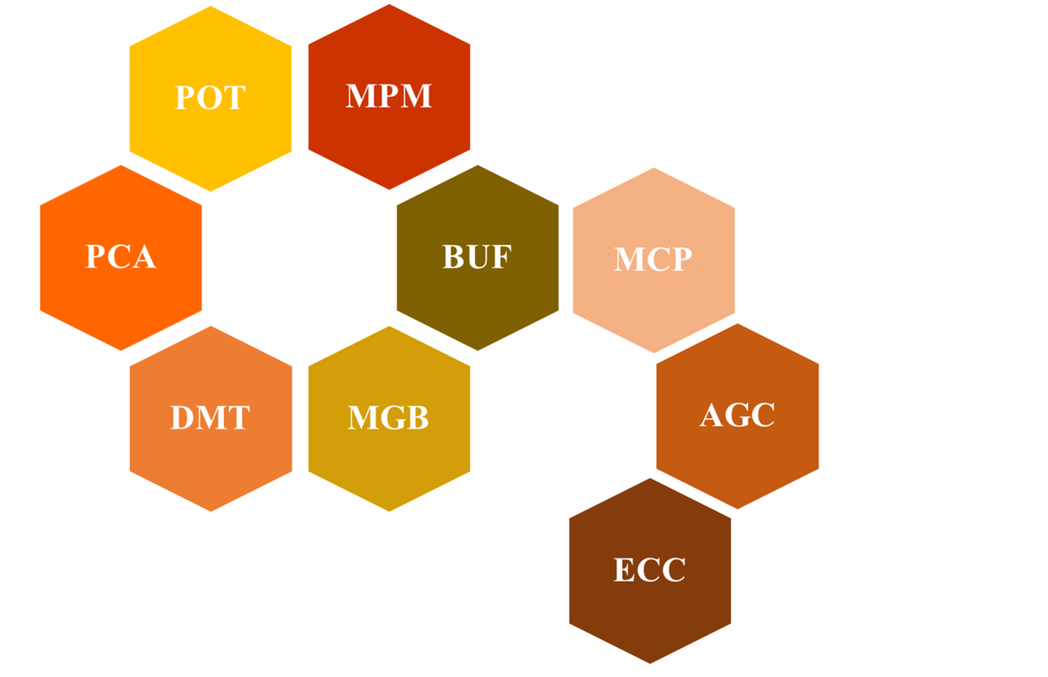

Apart from a complete memory testing and repair circuit development environment, START™ v3 also provides numerous micro architectures, such as Bottom-Up Flow (BUF), Multi-Chain Power Consumption (MCP), Auto-Gating Clock Cell Insertion Flow (AGC), Power_On Test (POT), Dynamic Memory Test (DMT), Memory Group By Definition (MGD), Memory Protection Mechanism (MPM), Power Consumption Analysis Mechanism (PCA) and Error Correcting Code (PCA).

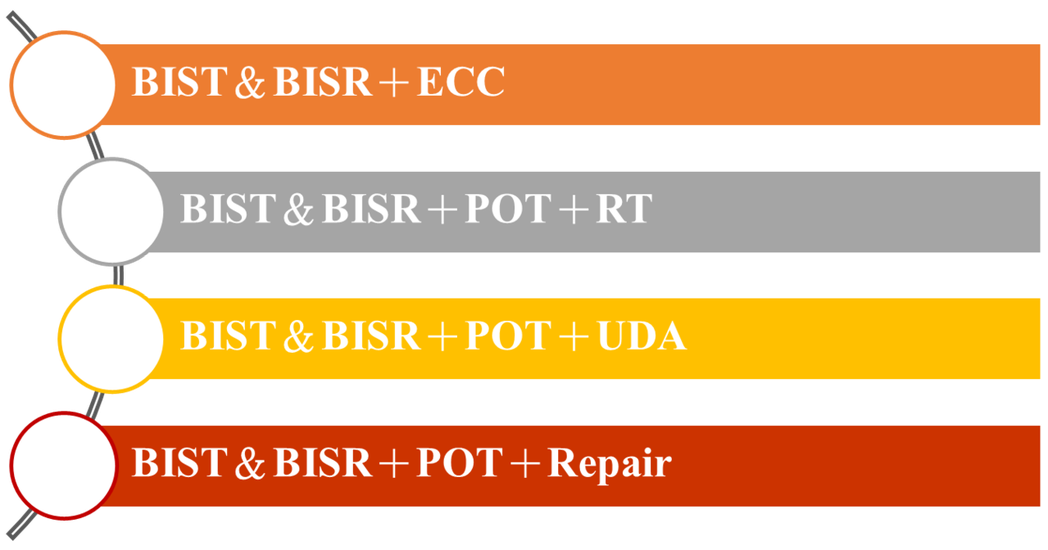

For automotive chips, START™ v3 also provides a variety of memory testing and repair solutions. First, BIST&BISR+ECC enables automotive chips to correct the memory errors during the system operation. Second, BIST&BISR+POT+RT can shorten the memory testing time when the chip is powered on and confirm the memory testing process simultaneously. Third, BIST&BISR+POT+UDA can execute customized memory testing algorithms to accurately detect the automotive chips with memory defects, so that the driving safety can be improved. Lastly, with BIST&BISR+POT+Repair, START™ v3 can perform large-scale memory repair when the range of memory defects in the automotive chip is too large, extending the automotive chips’ lifetime and improving driving safety.

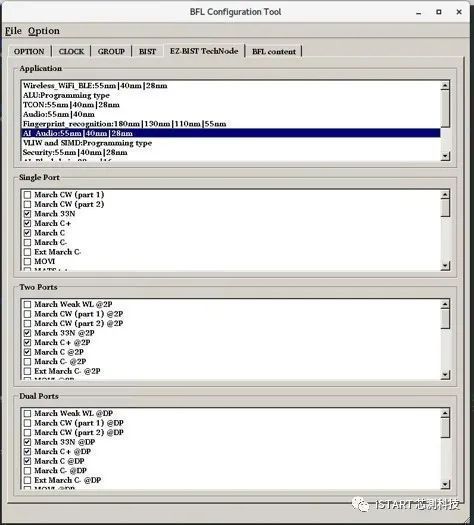

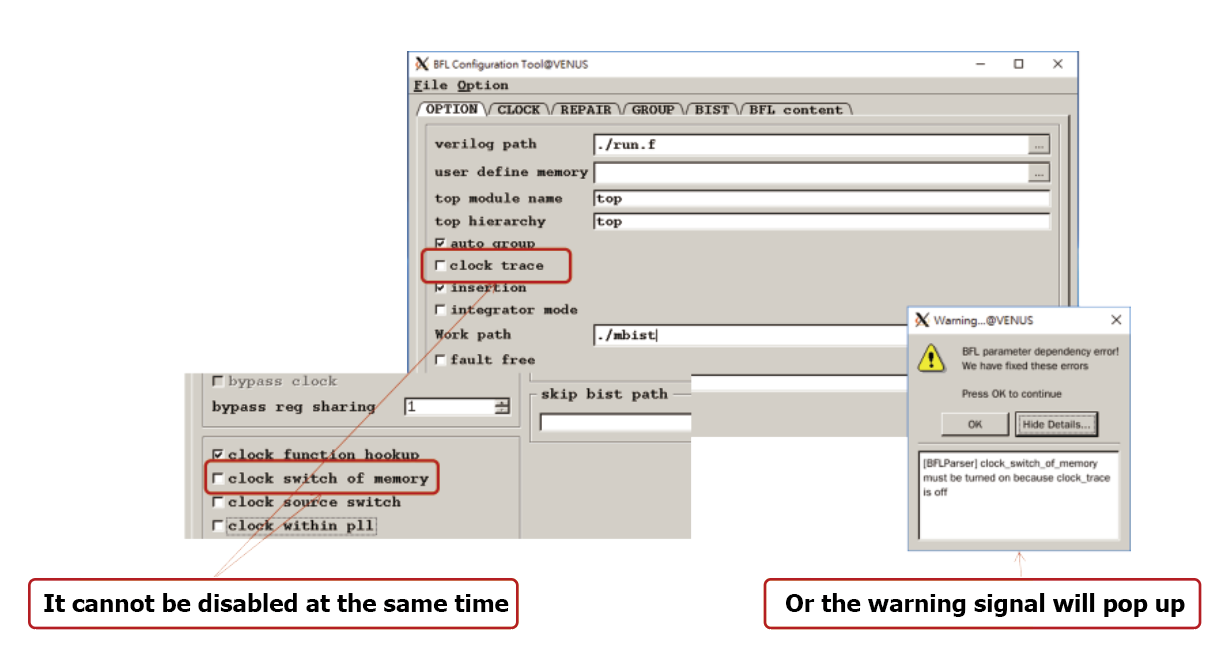

EZ-BIST (a memory testing circuit development environment) developed by iSTART-TEK is another EDA tool that is with a graphical user interface (GUI). It contains various memory testing algorithms. Through the GUI of EZ-BIST, IC design companies are able to select the most appropriate algorithms based on their chip development processes and chip applications, making the implementation of memory testing algorithm circuits more easily. In addition, the fool-proofing feature in EZ-BIST can prevent the errors caused by manual operation.

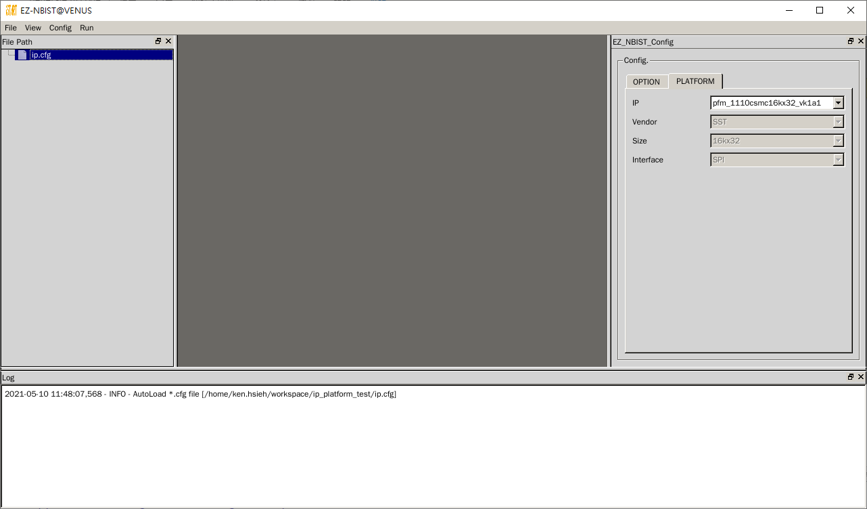

EZ-NBIST (a configurable non-volatile memory testing and repair circuit development environment) is also an EDA tool based on GUI and provides customized testing and repair solutions for non-volatile memories (NVM). MVM is a type of memory that keeps the data stored in it when the power is turned off. Thus, it can be used as a data storage element. OTP, MTP, eFlash, and ReRAM are all NVMs.

As said by iSTART-TEK, automotive chips must undergo precise memory testing before leaving the factory to ensure their reliability. IoT chips have stricter requirements of power consumption, cost and reliability. Currently most IoT chips require NVMs to reduce costs. EZ-NBIST can significantly reduce the NVM chip testing and repair time, simultaneously enhance the chip lifetime, and reduce the chip testing and repair costs.

Facing the severe challenges brought about by the U.S. Chip Act, the only way to maintain dominance in the semiconductor industry is to be self-reliant. iSTART-TEK has technological independence and patented technologies, diversified algorithms, efficient memory repair techniques, and simplified circuit areas, helping customers improve chip quality and competitiveness.

Enterprises had better consider using more professional, cost-effective EDA tools to develop high-quality, highly competitive chips, and iSTART-TEK’s specialized memory testing and repair technologies are the optimal solutions.